8 hours ago, rje said:

First, meaningful comparisons are done based on the whole system. So you have to take all of his videos into account.

It's more powerful than the C64. It has five times the voices, but no envelope control. 256 colors and VGA. 32 times the ROM. 8 times the RAM (for starters). Modern storage options.

Nowhere near as powerful as the MEGA 65, though.

I think the 8 Bit Guy also made some comparisons with Intel 286 systems, say somewhere around 12 Mhz, but that's with all the nifty features rolled in, NOT a raw performance comparison.

Commodore 64

Commodore 128

Commodore 65 (might approach the power of a low-end 8086, maybe)

Intel 8086 systems

Commander X16 ~~~ Intel 286 system

Intel 386SX

MEGA 65

C256 Fenix

Yeah, I did some comparison testing using my favorite prime number algorithm and an (allegedly) cycle accurate emulator. My results suggested about a 2.3:1 performance ratio (meaning the 6502 does in 1 clock cycle what the 8088 does in 2.3.)

The Z80 has a similar performance ratio, so in both cases, you can expect an 8MHz 6502 to be roughly equivalent to an 18MHz 8088 or Z80 computer.

This isn't because the 6502 is some sort of super chip. It's because the 6502 simply splits the clock into two phases, and it performs one operation per

phase, rather than one operation per

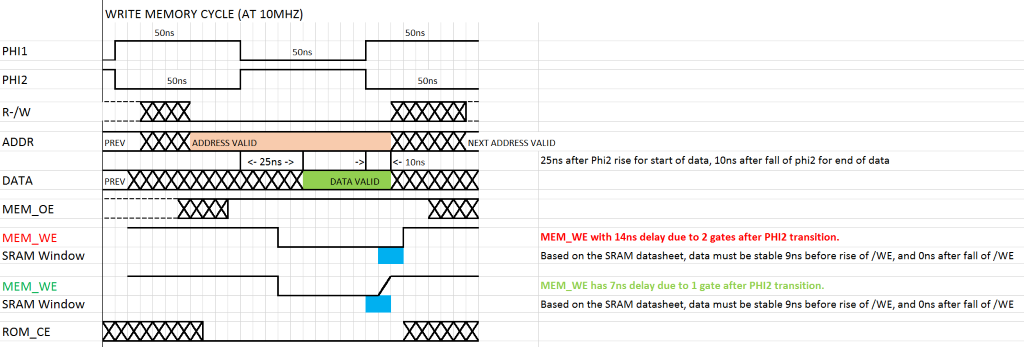

tick. Let's look at a memory read operation:

CPU Sets the address being accessed

Memory sets the data bus

CPU reads the data bus

On a Z80, this requires a minimum of 2 clock cycles (the instruction fetch): On the first cycle, the CPU sets the memory address, and the memory chips are expected to set the data bus on the falling edge of the clock. Then the CPU reads the data bus on the next cycle. Note the very short "IN" block in this diagram:

On the 6502, we don't deal in clock cycles, so much as

phases, called PHI1 and PHI2. Each clock tick has two phases, and each phase can have two operations happening. So during PHI1, the CPU is setting the address bus, and it can read the data bus during the second half of PHI2. So notice how the phases of a 6502 correspond almost exactly to the clock cycles of the Z80 or 8080.

This is why it's a little unfair to compare clock speeds of 6502 and 8088 systems, without taking the difference in cycle times into account. Since the 6502 doubles the clock internally, it's more correct to say the Commodore 64 has a

phase clock of 2MHz. And when you start looking at things from that perspective, the Z80 and 6502 suddenly are much more similar in terms of performance.

Having said all of that - the Z80 and 8088 still use extra cycles for instruction decoding. The 6502 actually has some primitive pipelining, and the instruction decode happens in parallel with the read of the first data byte of an instruction. This is the place where the 6502 is arguably better designed, since the Z80 uses two clock cycles to decode the opcode, and a minimum of 3 more ticks to fetch the first data byte (although there are several instructions that do not need operands.)

So while your typical single-operand Z80 instruction takes 5 clock cycles, the 6502 can do a single-operand operation in 2 clock cycles. Hence the myth that the 6502 is 2.5x more efficient than the Z80. It's actually not - it's just that you have to compare a 1MHz 6502 to a 2MHz Z80 to have a fair comparison.